SAJESM

- IJTAG Tool Suite (IEEE 1687)

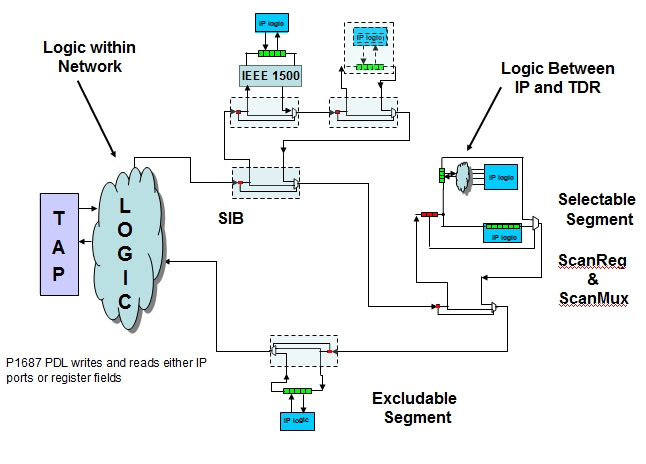

IJTAG-1687 has been created to standardize the access and interface of embedded Intellectual Property (IP). IJTAG defined two new languages: structural documentation in Instrument Connectivity Language (ICL) and documentation in a set of procedures in Procedural Description Language (PDL) . ICL defines the network from the IP to the JTAG logic. PDL defines the stimulus and reading the response directly to and from the IP block. Using these two languages, IJTAG can define complex reconfigurable access networks, how the IP are connected to the network, and describe the IP interface.

SiliconAid has a Full Suite of IJTAG tools which have been used by key development partners for years. This robust suite of IJTAG products are now available as a standard product as the standard is in the final review and has become stable. Our IJTAG Tool Suite supports the latest ICL and PDL syntax.

The SAJE IJTAG tool suite are chip focused tools to enable IP Providers, SOC designers and Integrators, Verification engineers, Validation engineers, Test and Product engineers, and Failure Analysis engineers to develop and leverage the IJTAG (IEEE 1687) standard. Our easy to use flow produces a self-checking simulation and also supports downstream formats to support Test ATE, Board Test, and System Testing.

The SAJE IJTAG tool suite can utilize compliant IP or analyze compliant IJTAG SOCs from all vendors. Compliant IP from multiple vendors or EDA companies is not a problem.

SiliconAid IJTAG Consulting Services focused on helping make your IP compliant and any other IJTAG related custom work required to optimize your IJTAG solution.

JTSTM

- (JTAG / IJTAG Insertion)

-

Creates all the

structures required for IJTAG compliant designs.

Compatible with any compliant JTAG controller from any EDA vendor or

custom design. User controlled SIB locations and IJTAG network creation. Creates all

connections to and from user selected IP and generates chip level ICL

file. Supports simple to complex user specified IJTAG structures

including multiple levels of IJTAG hierarchy.

JTVTM

- IJTAG : This is an optional feature that can be added to our flagship JTV

product to fully support IJTAG (IEEE 1687). This enables the Automatic Semantic &

Syntax checking, Verification, and Pattern Generation of IJTAG patterns using

ICL and PDL. JTV-IJTAG also will traverses the IJTAG network(s) to verify all network

possibilities and generates the associated tests.

JTNTM

: Automatically & Intuitively draws the IJTAG network graphically. Allowing the

user to visualize the network, select instruments for pattern generation, select

different tests, analyzes and

optimizes the network, and intelligently retargets patterns to the chip level.

JTN provides the user with the flexibility to configure the network on the fly

for greater and faster debug.

JTNTM

: Automatically & Intuitively draws the IJTAG network graphically. Allowing the

user to visualize the network, select instruments for pattern generation, select

different tests, analyzes and

optimizes the network, and intelligently retargets patterns to the chip level.

JTN provides the user with the flexibility to configure the network on the fly

for greater and faster debug.

JTDTM

: Interactive and intuitive JTAG debugger that drives hardware via the JTAG

interface. JTD will interface with JTN to instantly apply new IJTAG patterns to

the Chip JTAG interface.

IJTAG Consulting Services : (IJTAG-1687 and IJTAG-1149.1-2013) Leveraging over 15 years of DFT consulting on your IJTAG related challenges. Senior Engineers that know and understand IJTAG networks and architectures. Providing world-class services on your custom IJTAG requirements. Assisting in generating ICL and PDL for in-house or third-party IP and much more.